ISA是IndustryStandardArchitecture的缩写ISA插槽是基于ISA总线(IndustrialStandardArchitecture,工业标准结构总线)的扩展插槽,其颜色一般为黑色,比PCI接口插槽要长些,位于主板的最下端。其工作频率为8MHz左右,为16位插槽,最大传输率16MB/sec,可插接显卡,声卡,网卡已及所谓的多功能接口卡等扩展插卡。其缺点是CPU资源占用太高,数据传输带宽太小,是已经被淘汰的插槽接口。

ISA是8/16bit的系统总线,最大传输速率仅为8MB/s,但允许多个CPU共享系统资源。由于兼容性好,它在上个世纪80年代是最广泛采用的系统总线,不过它的弱点也是显而易见的,比如传输速率过低、CPU占用率高、占用硬件中断资源等。后来在PC‘98规范中,就开始放弃了ISA总线,而Intel从i810芯片组开始,也不再提供对ISA接口的支持。

ISA卡外观

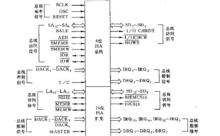

2ISA总线时序

ISA总线是IBMPC/AT机(CPU是80286)所用的系统总线.。PC/AT总线经过标准化之后的名称。IEEE将ISA总线作为IEEEP996推荐标准。这是一个16位兼8位的总线标准。如果忽略标准化细节则可认为16位ISA总线就是PC/AT总线。由于IBMPC/AT与IBMPC、IBMPC/XT机(CPU都是8088)所用的Pc总线兼容,所以可认为8位ISA总线(16位ISA总的低8位部分)就是PC总线。

ISA总线的时序和80868088的时序基本相同但也有一些区别。有了8086/8088时序基础对ISA总线时序的理解主要在于以下几点

①地址和数据已不再分时复用信号线因此在整个总线周期内有效。

②和8086/8088的最大模式一样,存储器读/写和I/O读/写的控制信号已分开,进行一种操作只需一个控制信号。

③一个典型的存储器读/写周期还是由T1、T2、T3和T4组成,而I/O读写周期和DMA周期都自动插入了一个等待时钟周期。

④I/OCHRAY相当于8086/8088时序中的READY信号。当总线板卡上

的存储器或I/0电路较慢时,可利用该信号迫使CPU插入等待时钟周期。但等待时钟周期不得超过10个。

⑤8位ISA总线在存储器读/写周期可用到20位地址,而16位ISA总线在存储器读写周期中可使用24位地址。但由于受I/O指令的限制。8位和16位ISA总线的I/0读/写周期都只能使用低16位地址。

⑥BALE在CPU总线周期的T1期间有效,它的基本作用是进行地址锁存。但也可以作为一个新的CPU总线周期已开始的标志。

⑦AEN有效表示DMAC正在控制系统总线所以它可以作为系统处于DMA总线周期的标志。

3ISA总线接口

执行ISA总线规范的电路称为。ISA总线接口。通过ISA总线接口可以为系统扩充存储器。也可以扩充I/O设备。在实际应用中对后者的需求更大因为机器主板上一般已经或者可以安装足够的存储器而I/O设备是各种各样的。系统对I/O设备的需求也不尽相同。正因为如此,ISA总线又被归类于I/O扩展总线。注意I/O设备是一个广义的概念可以是像打印机、硬盘那样实实在在的设备。也可以是像A/D转换器、D/A转换器、计数器那样的电路。当

I/O设备是一个电路时。通常和总线接口做在一个总线板卡上习惯称之为某某接口板(如A/D接口板)或某某接口(如D/A接口)。从ISA总线的引脚信号以及总线时序看和8086/8088最大模式时的系统三总线以及8086/8088的总线周期时序差别不大,因此在设计ISA总线接口特别是I/O接口时。除了下面三点需要注意外,可以采用与设计8086/8088

接口几乎相同的方法。这三点是

1.当设计非DMA方式的I/O接口时,应把AEN为低作为该接口工作的使能

条件。以确保在总线上进行DMA传送时该接口不工作,否则DMA传送时所发出的

地址与该接口设计地址相同时该接口会误操作。

2.系统对ISA总线上的I/O端口地址采用部分译码方法。只译码A9、AO或

A10、A0。在选择接口地址时应避开系统已占用的地址以及它们的重叠区。

3如果所要设计的接口中包含需要CPU插入等待时钟的功能则需设计

一个I/0CHRAY产生电路。以便在必要时使总线上的I/OCHRAY线为低电平。

但该电路与总线上的I/OCHRAY线的电气连接以及有效信号出现和持续时

间等方面有一些要求,实际应用时需再参阅其详细资料。